electronics-journal.com

18

'26

Written on Modified on

Renesas Introduces 3nm TCAM for Automotive SoCs

Configurable 3nm FinFET TCAM achieves 5.27 Mb/mm² density, 0.167 fJ/bit search energy and enhanced functional safety for automotive and high-speed networking applications.

www.renesas.com

In automotive SoCs, networking infrastructure and high-speed data processing systems, ternary content-addressable memory (TCAM) must combine high density, fast search performance and low energy consumption while meeting functional safety requirements. Renesas Electronics Corporation has developed a configurable TCAM built on a 3nm FinFET process that addresses these constraints through a hybrid macro architecture, pipelined search optimization and safety-oriented memory design. The technology was presented at the International Solid-State Circuits Conference 2026 (ISSCC 2026), held February 15–19 in San Francisco, USA.

The new TCAM targets large-scale configurations such as 256-bit × 4,096 entries, which are increasingly required in 5G infrastructure, cloud and edge computing, and advanced automotive electronics.

Flexible configuration with integrated hard- and soft-macro architecture

Conventional TCAM scaling typically relies on fixed hard macros. As configurations grow, this approach increases peripheral circuitry such as banks and repeaters, enlarges area and complicates timing closure, while also raising search power.

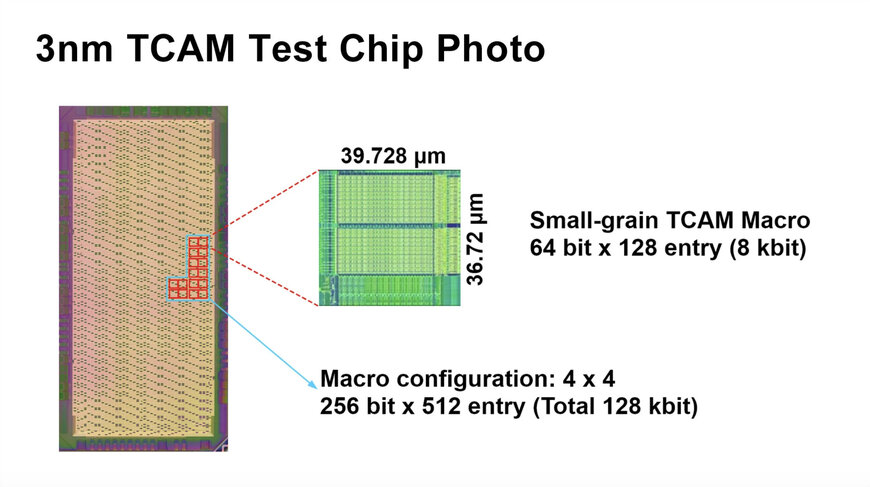

Renesas addresses this limitation by combining fine-granularity hard macros with tool-driven soft-macro auto-generation. The hard macros support search key widths from 8 to 64 bits and entry depths from 32 to 128 entries. Larger configurations are constructed by combining these elements into a configurable single macro on chip.

This architecture achieves a reported memory density of 5.27 Mb/mm², enabling compact integration of large TCAM arrays in advanced SoCs.

Pipelined search with energy reduction mechanisms

Each hard macro integrates an all-mismatch detection circuit that evaluates search results in a first stage and determines whether a second search stage is required. The TCAM executes a two-stage pipelined search, halting the second stage when no match is possible, thereby reducing unnecessary switching activity.

In 64–256-bit × 512-entry configurations, the design reduces search energy by:

- Up to 71.1% using column-wise pipelined search with key partitioning for keys larger than 64 bits

- Up to 65.3% using row-wise pipelined search without key partitioning for keys up to 64 bits

For a 256-bit × 512-entry configuration, the TCAM achieves a search energy of 0.167 fJ/bit and operates with a 1.7 GHz search clock. The resulting figure-of-merit, defined as density × speed ÷ energy, reaches 53.8, exceeding previously published results.

Functional safety enhancements for automotive integration

Automotive SoCs require compliance with standards such as ISO 26262, which impose strict safety coverage requirements. In TCAM arrays, bitcells corresponding to the same address are physically adjacent, meaning that soft errors may affect two bits simultaneously. Conventional SECDED (Single Error Correction, Double Error Detection) error correction cannot correct such double-bit faults.

Renesas mitigates this risk through two architectural measures:

Functional safety enhancements for automotive integration

Automotive SoCs require compliance with standards such as ISO 26262, which impose strict safety coverage requirements. In TCAM arrays, bitcells corresponding to the same address are physically adjacent, meaning that soft errors may affect two bits simultaneously. Conventional SECDED (Single Error Correction, Double Error Detection) error correction cannot correct such double-bit faults.

Renesas mitigates this risk through two architectural measures:

- Splitting odd and even data buses for user data and ECC parity to increase physical separation of memory cells. This reduces the probability that a single soft error results in an uncorrectable double-bit failure.

- Implementing dedicated SRAM for ECC parity with an address decoder independent of the TCAM array. This improves error detectability when incorrect addresses are written.

These measures increase fault detectability and correction capability, strengthening functional safety coverage in automotive applications.

Application scope beyond networking

While TCAM has traditionally been associated with networking equipment, the combination of configurable key widths, scalable entry depth, reduced search energy and enhanced safety enables its integration into automotive SoCs for applications such as ADAS data routing, in-vehicle networking and sensor data classification.

The architecture is also suitable for industrial and consumer systems requiring high-speed data exchange between sensors and processors, where energy efficiency and timing determinism are critical.

By integrating density optimization, pipelined search efficiency and safety-aware memory design in a 3nm FinFET process, Renesas extends TCAM applicability from high-performance networking to automotive-grade system-on-chip platforms.

www.renesas.com

Application scope beyond networking

While TCAM has traditionally been associated with networking equipment, the combination of configurable key widths, scalable entry depth, reduced search energy and enhanced safety enables its integration into automotive SoCs for applications such as ADAS data routing, in-vehicle networking and sensor data classification.

The architecture is also suitable for industrial and consumer systems requiring high-speed data exchange between sensors and processors, where energy efficiency and timing determinism are critical.

By integrating density optimization, pipelined search efficiency and safety-aware memory design in a 3nm FinFET process, Renesas extends TCAM applicability from high-performance networking to automotive-grade system-on-chip platforms.

www.renesas.com